Author: SemiconShorts

-

Wrapper Chains

The major part of DFT is converting a design into a scannable design where all the flip flops are connected in a network of scan chains. With more complex designs, and many scan chains to handle, hierarchical DFT comes into play. This methodology involves wrapper chain structure, which will be discussed here. Wrapper chains are…

-

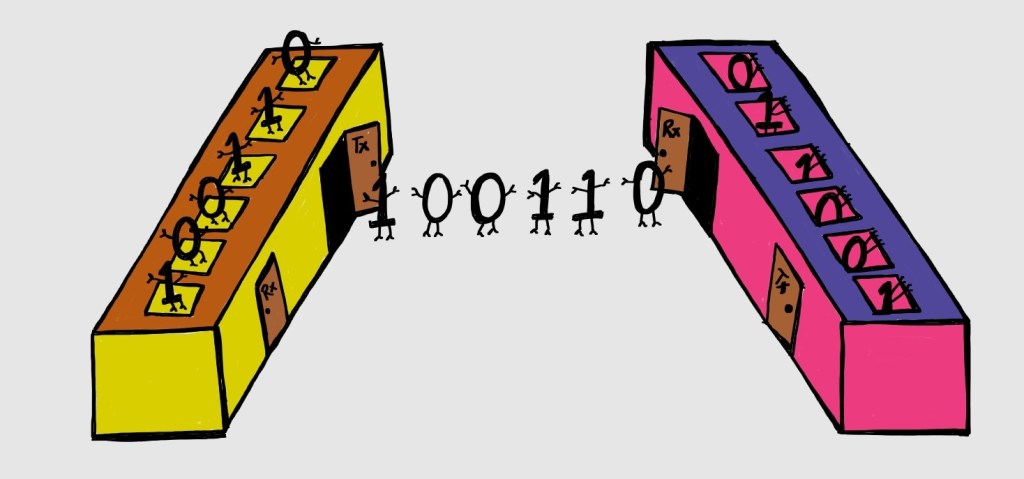

UART

UART – ‘Universal Asynchronous Receiver Transmitter’ is a communication hardware, which utilizes only 2 pins to transfer data across devices. Let us discuss this one of the most used and earliest communication protocols. Asynchronous communication Serial Full duplex Uses two wires to transfer data: Transmitter (Tx) and Receiver (Rx) 1 to 1 communication Data is…

-

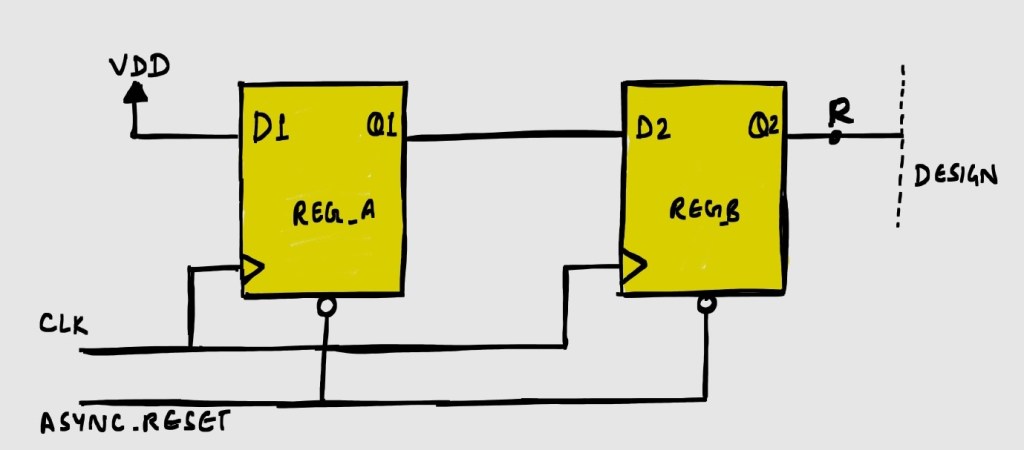

Reset Synchronizer

Resets are one of the most critical signals in a design. ‘What is a reset?’ discusses all the basics about them. An issue with asynchronous reset was mentioned in this article, which is, de-assertion of asynchronous reset. If this de-assertion occurs close to an active clock edge, it violates the timing and causes metastability. There…

-

Advanced High-Performance Bus – AHB

There are many functional blocks in an SoC, which need to communicate with each other. AMBA (Advanced Microcontroller Bus Architecture) is one such specification by ARM, which defines on-chip communication standards. AHB and APB are two distinct buses under AMBA. An example of an AMBA system is given in Figure 1. We will focus on …

-

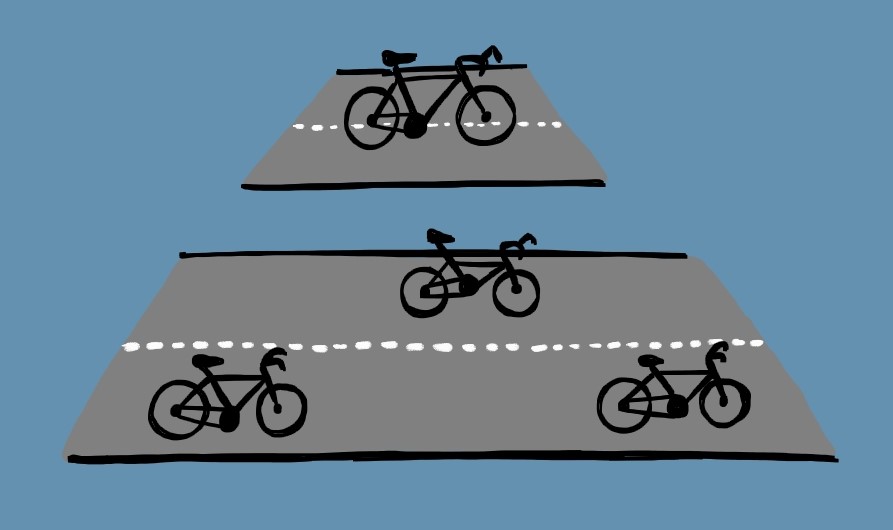

Multicycle Path

Multicycle paths are another kind of timing exception like false paths. Generally, data launched from one flop reaches the next flop in one clock cycle. But there may be cases where it takes more than one clock cycle to reach the destination flop. Such paths are termed as ‘Multicycle paths’. This can be due to…

-

4 Bit Up-Counter

When we talk about digital design, the language we use are HDLs (Hardware Description Language). Verilog is one such language which is used to create most of the designs. To get started with Verilog, lets study a simple 4 bit up-counter. Function: This counter is a 4 bit counter, i.e. it can count up to…

-

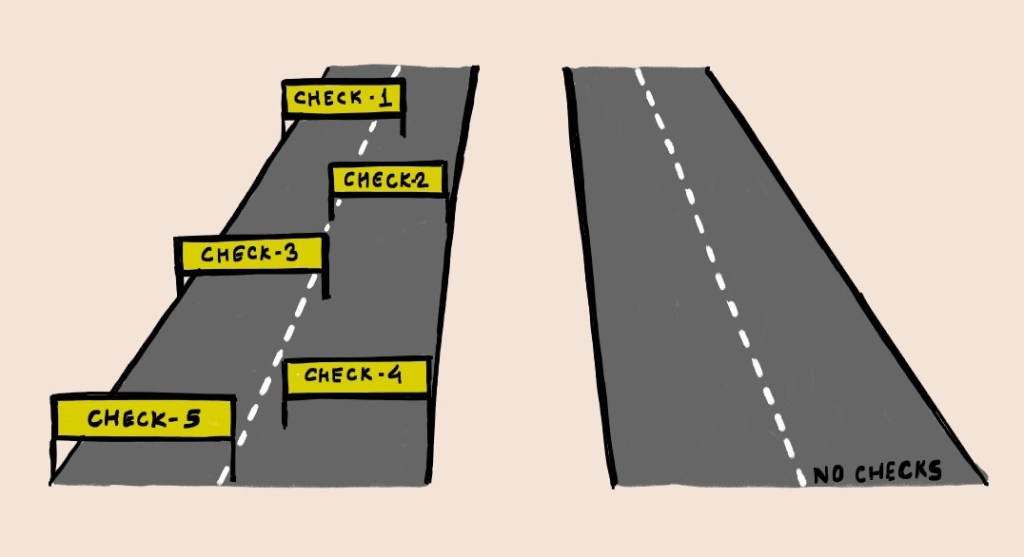

False Path

While setting up timing constraints for different paths in the design, there are some paths which need special attention. The timing needs to be relaxed, and hence these are called Timing Exceptions. One such exception is ‘False paths’, which is discussed here. Generally, a launch flop transmits a signal, which needs to be captured in…

-

Timing verification – III

Examples of Setup/hold violations and How to fix those Setup Violation Tcq = 0.1ns = 100ps Tcomb = 0.9ns = 900ps Tperiod = 1ns Tsetup = 0.1ns = 100ps Tskew = 0.15ns = 150ps Tuncertainty = 0.25ns = 250ps Arrival Time = Tcq + Tcomb = 0.1 + 0.9 ns = 1 ns Required Time…

-

Timing Verification – II

Timing Paths The basics of timing verification have been covered in the article ‘Timing verification – I‘. Please go through ‘setup and hold time‘ to refresh your concepts. This article will focus on the timing paths. There are four kinds of timing paths that can be found in a design: Primary input to the data…

-

Timing Verification – I

Introduction to STA There are certain timing specifications associated with the design, which are tested during ‘timing verification’. Timing is an integral part of chip designing and it basically separates a hardware and software code. It also determines the maximum frequency at which a design can operate. Functional verification does not consider propagation delays and…